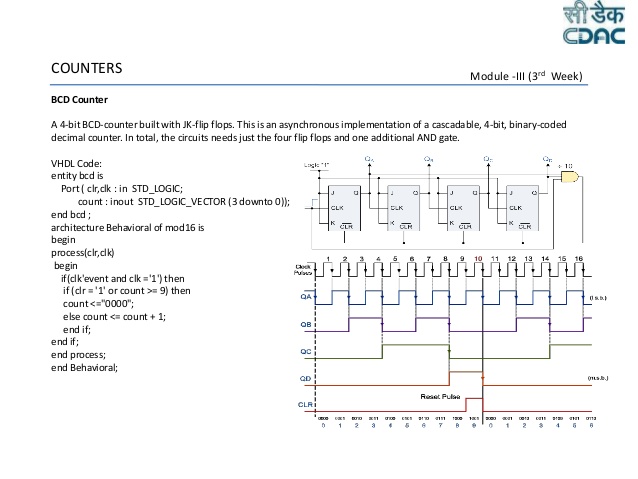

I'm trying to build an 8bit counter in Verilog. I specifically need to create a module that I instantiate 8 times. I have followed the diagram below (and assumed that I can just build on it to make it 8 instead of 4 bits). It appears what I have built instead is a shift register, it can shift ones and zeros - instead of 0001 - 0011 I need 0001 - 0010 (duh!). I feel as though I have misinterpreted the circuit diagram, as my logic seems otherwise sound. Any help much appreciated!TFlipFlop: module tflfl(t, clk, clr, q);input t;input clk;input clr;output reg q;always@(posedge clk, negedge clr)beginif(clr)q.

Your schematic shows a T-type flip-flop, which toggles when its input is high. Your rtl code, on the other hand, implements a regular D-type flip-flop.

Your module should instead read: always@(posedge clk, negedge clr)beginif(clr)q.

Dec 23, 2018 Click to share on Twitter (Opens in new window) Click to share on Facebook (Opens in new window).

In this Verilog tutorial, we implement a basic Ripple Carry Counter design and test using Verilog.Complete Ripple Carry Counter from the Verilog tutorial:Recommend viewing in 720p quality or higher.About EDA Playground:EDA Playground is a web browser-based integrated development environment (IDE) for simulation of SystemVerilog, Verilog, VHDL, and other HDLs. EDA Playground is a free web application that allows users to edit, simulate, share, synthesize, and view waves for hardware description language (HDL) code.